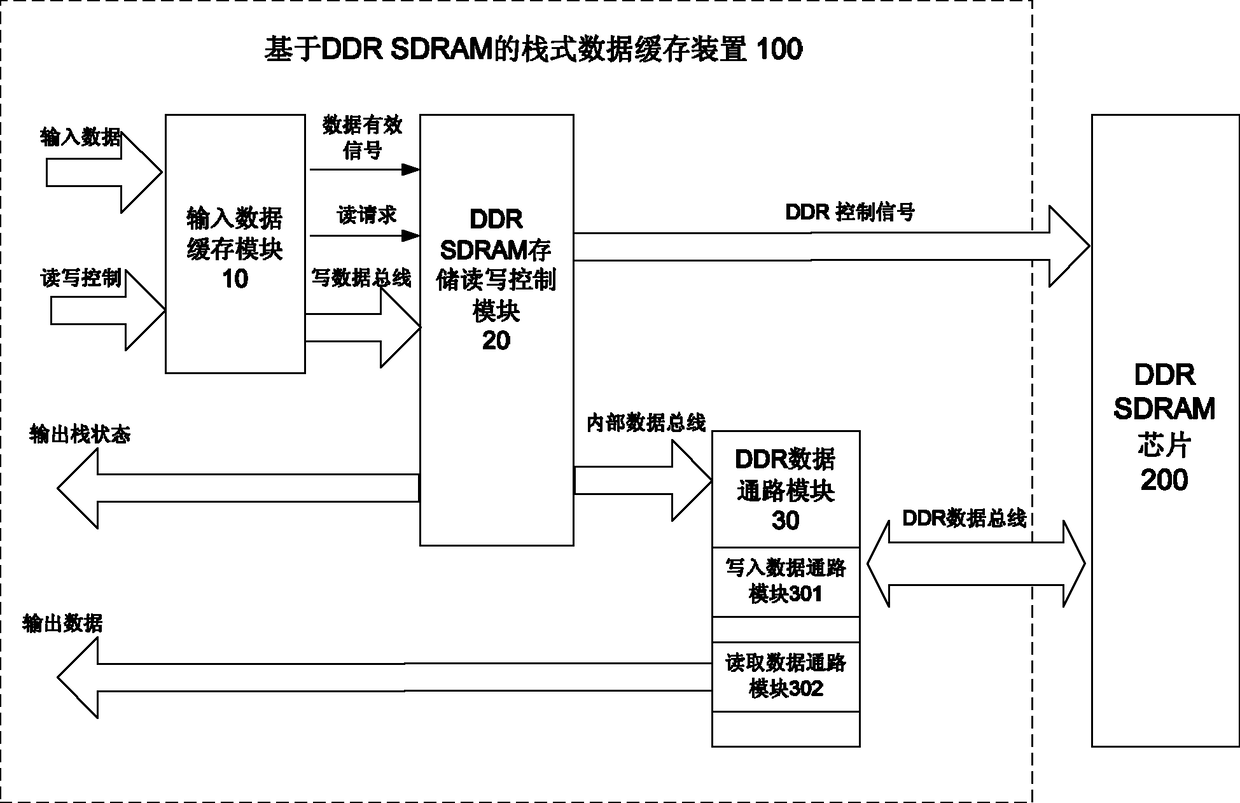

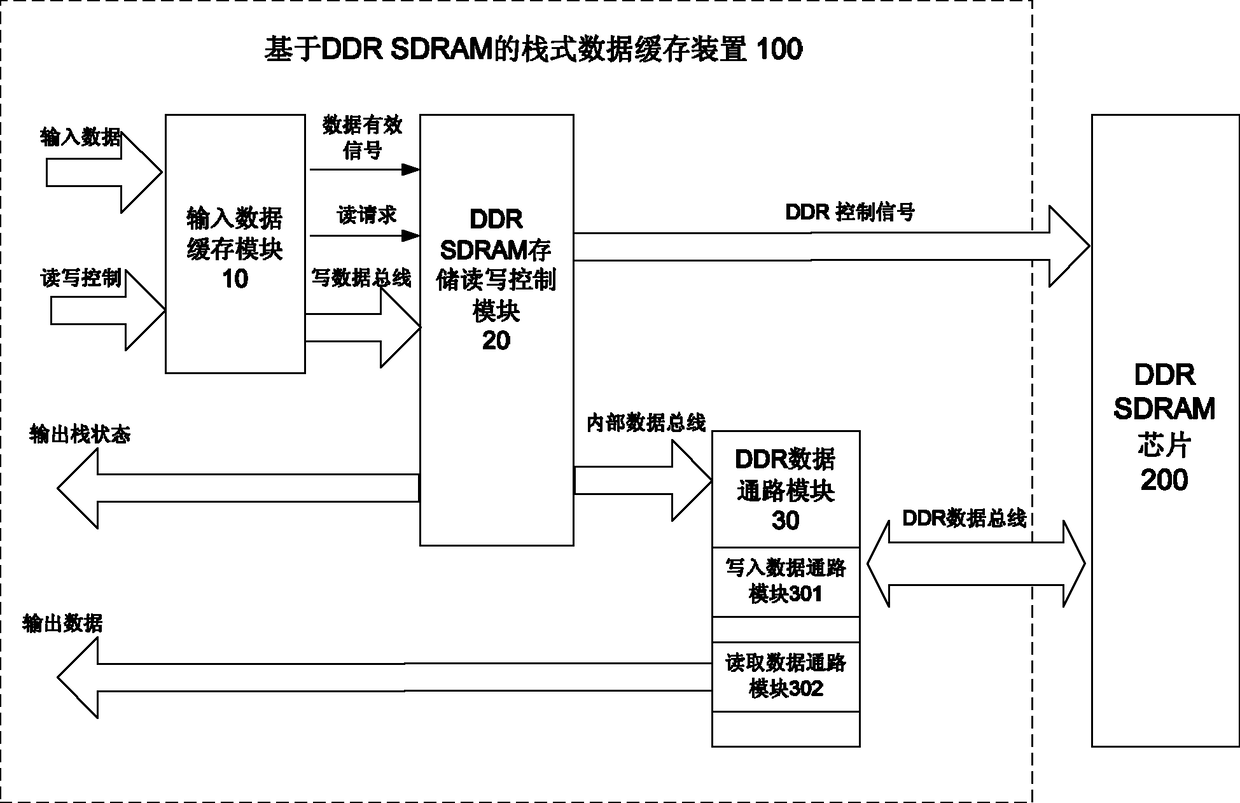

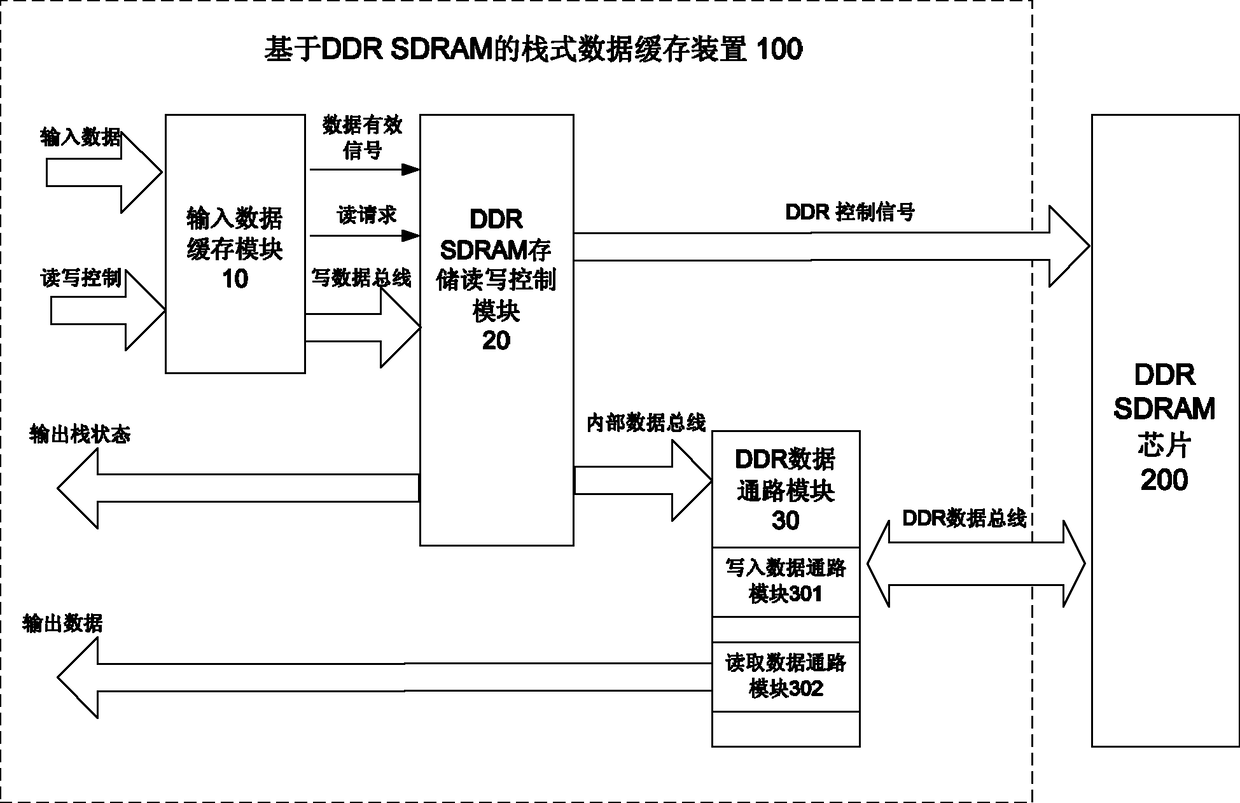

1.一种基于DDR SDRAM的栈式数据缓存装置,其特征在于,包括:输入数据缓存模块,用于为写入DDR SDRAM的数据提供缓存;DDR SDRAM存储读写控制模块,连接所述输入数据缓存模块,用于对DDR SDRAM进行控制,向用户呈现以页面为单位,按照栈的方式进行数据的读写,其中,该DDR SDRAM的存储单元的编址格式为行地址位于高位,列地址位于低位;DDR数据通路模块,连接所述DDR SDRAM存储读写控制模块,用于根据所述DDR SDRAM存储读写控制模块的读写控制,实现单边沿数据和双边沿数据之间的转换。

2.根据权利要求1所述的基于DDR SDRAM的栈式数据缓存装置,其特征在于,所述输入数据缓存模块进一步包括:用于缓存用户写入的数据的异步FIFO,所述异步FIFO大小为SDRAM的两个页面大小。

3.根据权利要求2所述的基于DDR SDRAM的栈式数据缓存装置,其特征在于,所述异步FIFO每接收完成一个页面的数据,所述输入数据缓存模块将与所述DDR SDRAM存储读写控制模块相连的数据有效信号置位,触发所述DDR SDRAM存储读写控制模块启动一次DDR SDRAM写操作;对DDR SDRAM的页面读请求,则直接转发至所述DDR SDRAM存储读写控制模块处理。

4.根据权利要求1所述的基于DDR SDRAM的栈式数据缓存装置,其特征在于,所述DDR SDRAM存储读写控制模块进一步包括:初始化子模块,用于完成DDR SDRAM上电复位后的初始化构成;栈读写指针控制子模块,连接所述初始化子模块,用于接收所述初始化子模块发出的初始化完成信号,通过栈顶指针对DDR SDRAM的数据写入和读出进行存取控制;读写及刷新控制子模块,连接所述初始化子模块、所述栈读写指针控制子模块,用于接收所述初始化子模块发出的初始化完成信号,并根据所述栈读写指针控制子模块提供的读写请求和读写的页面地址,对DDR SDRAM进行读写控制,并实现DDR SDRAM自动刷新的正确性。

5.根据权利要求4所述的基于DDR SDRAM的栈式数据缓存装置,其特征在于,所述栈读写指针控制子模块以后入先出的存取方式管理DDR SDRAM的数据写入和读出,并对栈满和空状态进行判断,当栈非满时,向DDR SDRAM中写入数据,当栈未空时,从DDR SDRAM中读出数据。

6.根据权利要求4所述的基于DDR SDRAM的栈式数据缓存装置,其特征在于,所述读写及刷新控制子模块通过单次8字节突发传输之间的无缝连接,实现页面式的突发传输,通过动态刷新时间间隔,保证页面突发传输不间断情况下DDR SDRAM自动刷新的正确性。

7.根据权利要求1所述的基于DDR SDRAM的栈式数据缓存装置,其特征在于,所述DDR数据通路模块进一步包括:读取数据通路模块,用于将从DDR SDRAM读取的双边沿8位数据转换为单边沿16位数据;写入数据通路模块,用于将向DDR SDRAM写入的单边沿16位数据转换为双边沿8位数据。

8.一种如权利要求1-7任一所述装置实现的基于DDR SDRAM的栈式数据缓存方法,所述装置按照栈的方式进行数据的读写,其特征在于,包括:步骤一,所述装置在上电复位后对DDR SDRAM进行初始化,其中,DDR SDRAM的模式寄存器将DDR SDRAM设置为8字节突发读写模式;步骤二,所述装置进入系统空闲状态,判断用户的操作类型,其中栈数据缓存装置中的数据写操作优先于数据读操作,若操作类型为写入操作,则进入步骤三,若操作类型为读取操作,则进入步骤四;步骤三,判断栈是否已满,若栈已满,则不能进行数据写入操作,置写入操作失败,转入步骤二;若栈非满,则跳转至步骤五;步骤四,判断栈是否为空,若栈空,则不能进行数据读出操作,置读取操作失败,转入步骤二;若栈非空,则跳转至步骤六;步骤五,以页面为单位写入数据,连续启动Burst为8的DDR SDRAM写操作;步骤六,以页面为单位读出数据,连续启动Burst为8的DDR SDRAM读操作。

9.根据权利要求8所述的基于DDR SDRAM的栈式数据缓存方法,其特征在于,所述步骤五中,包括:当写入次数达到2(logP-3)时,转入步骤二,其中P为页面的大小,logP为以2为底,P的对数。

10.根据权利要求8所述的基于DDR SDRAM的栈式数据缓存方法,其特征在于,所述步骤六中,包括:当读取次数达到2(logP-3)时,转入步骤二,其中P为页面的大小,logP为以2为底,P的对数。

展开

北京

北京

微信公众号 扫一扫 关注我们

微信公众号 扫一扫 关注我们