- 技术(专利)类型 发明专利

- 申请号/专利号 CN200410004593.5

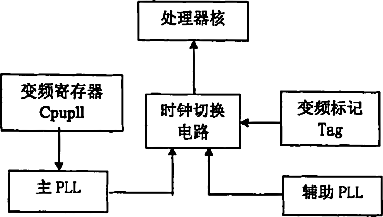

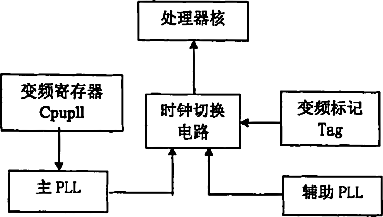

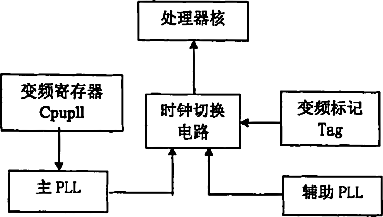

- 技术(专利)名称 一种SOC架构下的处理器核动态变频装置和方法

- 项目单位 中国科学院计算技术研究所

- 发明人 张志敏

- 行业类别 物理

- 技术成熟度 详情咨询

- 交易价格 ¥面议

- 联系人 李志文

- 发布时间 2021-07-15

北京

北京

客服热线:010-83278899

微信公众号 扫一扫 关注我们

微信公众号 扫一扫 关注我们

项目简介

说明书

企业营业执照

专利注册证原件

身份证

个体户营业执照

身份证

专利注册证原件

专利代理委托书

转让申请书

转让协议

手续合格通知书

专利证书

专利利登记簿副本

提交