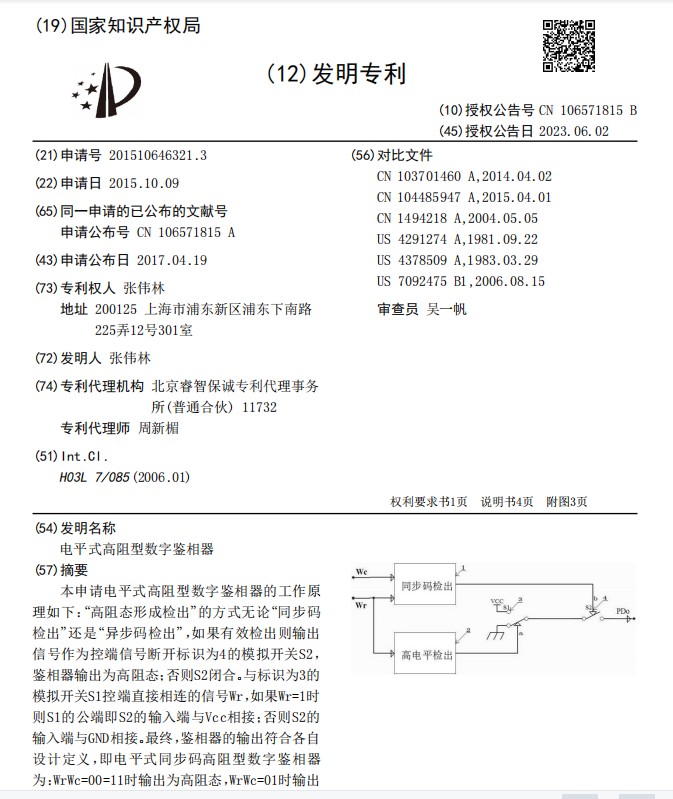

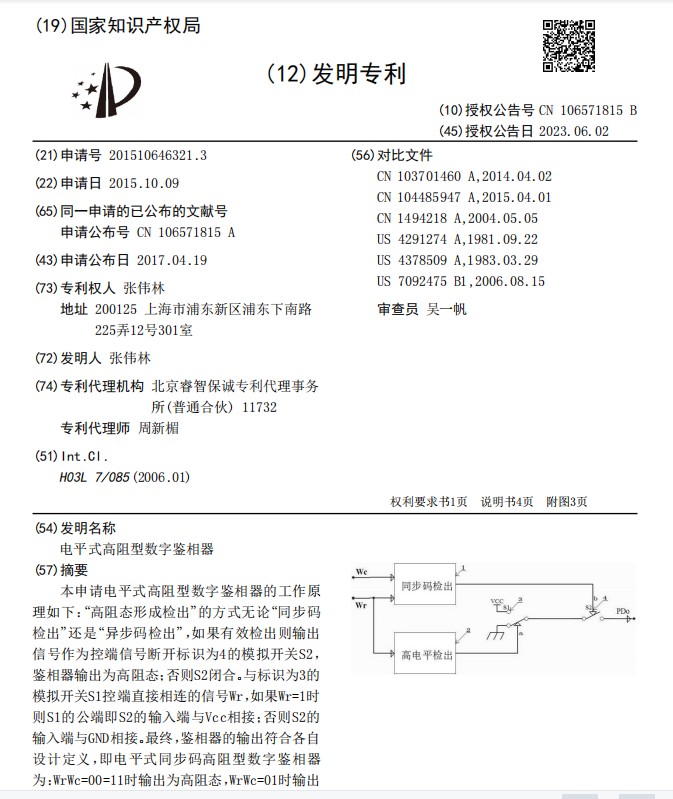

- 技术(专利)类型 发明专利

- 申请号/专利号 201510646321.3

- 技术(专利)名称 电平式高阻型数字鉴相器

- 项目单位

- 发明人 张伟林

- 行业类别 人类生活必需品

- 技术成熟度 详情咨询

- 交易价格 ¥面议

- 联系人 张伟林

- 发布时间 2023-06-27

北京

北京

客服热线:010-83278899

微信公众号 扫一扫 关注我们

微信公众号 扫一扫 关注我们

项目简介

本申请电平式高阻型数字鉴相器的工作原理如下:“高阻态形成检出”的方式无论“同步码检出”还是“异步码检出”,如果有效检出则输出信号作为控端信号断开标识为4的模拟开关S2,鉴相器输出为高阻态;否则S2闭合。与标识为3的模拟开关S1控端直接相连的信号Wr,如果Wr=1时则S1的公端即S2的输入端与Vcc相接;否则S2的输入端与GND相接。最终,鉴相器的输出符合各自设计定义,即电平式同步码高阻型数字鉴相器为:WrWc=00=11时输出为高阻态,WrWc=01时输出为“0”态值,WrWc=10时输出为“1”态值;电平式异步码高阻型数字鉴相器为:WrWc=01=10时输出为高阻态,WrWc=00时输出为“0”态值,WrWc=11时输出为“1”态值。

说明书

本发明所涉及的内容与电路形式,其理论在现有发行刊物与书籍中并不存在,所依据的理论是发明者本人编写的专著《PLL设计的理论与应用》中的第4.7节《电平式三态类异步码高阻型相位比较器的设计与时序分析》及第4.8节《电平式三态类同步码高阻型相位比较器的设计与时序分析》中相关内容。所依据的设计方式是采用了发明名称为《标准化设计高阻型数字鉴相器的结构原理方案》中规定的方法。电平式高阻型数字鉴相器,这是一个全新概念的鉴相器。

本发明所涉及的电路形式不仅适合于通用型数字或模拟IC芯片组建数字鉴相器,更适合应用于集成化电路设计的高阻型数字鉴相器电路中。

现有高阻型数字鉴相器仅有一种形式,其中之一型号为图1所示的74HC4046的IC中上升边沿触发式数字鉴相器,分析其设计时的输入输出信号间工作定义即规定可以归纳为如下:

a.初态

每一次复位后鉴相器都回归到初态这一常态,标志为WrWc(=QrQc)=00,鉴相器输出PDo=高阻态。

b.D触发器的工作特征

输入信号Wr与Wc有着各自独立的上升边沿触发式D触发器,处在初态即Q=“0”码的D触发器一旦有上升边沿触发,触发器输出为Q=“1”码。这种输出状态保持到复位条件形成为止,一旦复位后触发器输出回归到Q=“0”码;即Q=“1”是过渡态不是常态。

c.触发器输出Q=“1”码时的最短时间至少有形成复位信号输出所需最短时间即图1中与非门的一个周期的工作时间,与D触发器复位所需的一个周期的工作时间之和。

d.鉴相器输出状态取决于D触发器输出Q值这一电平值所决定的,即是由QrQc码值状态所决定的。设计定义初态QrQc=11时PDo=高阻态;有相位检出即边沿有效触发时如果QrQc=01则PDo=“H”态,如果QrQc=10则PDo=“L”态;相位检出结束的标志是QrQc=00这一过度状态,规定PDo=高阻态。

由此,图1中A所指的电路部分构成了一个完整电平式高阻型数字鉴相器的雏形。

本发明中涉及二种形式的电平式高阻型数字鉴相器,一种是电平式同步码高阻型数字鉴相器(以下简称为同步码鉴相器),为图2所示的电路方框图;另一种是电平式异步码高阻型数字鉴相器(以下简称为异步码鉴相器),为图3所示的电路方框图;都是基于专利申请号为2015106449019的《标准化设计高阻型数字鉴相器的结构原理方案》中的规定方法设计的。作为具体实现电路的案例,图4为一个电平式同步码高阻型数字鉴相器的电路图,图5为一个异步码高阻型数字鉴相器的电路图。

首先作为一个名词的解释,测试法是指二个串联电阻其二端分别接鉴相器供电电源的二端,其中点接鉴相器的输出(端)PDo并作为测试电路的输出端,这就是测试法下鉴相器输出端的连接方法。

图1是摘录自该芯片厂商的数据手册,内中A部分电路是一个同步码鉴相器的雏形。

图2为本发明内容的同步码鉴相器的结构原理方案。

图3为本发明内容的异步码鉴相器的结构原理方案。

图4是作为一个具体的同步码鉴相器实现形式的电路图。

图5是作为一个具体的异步码鉴相器实现形式的电路图。

图6是电平式同步码鉴相器的信号关系仿真图。

图7是电平式异步码鉴相器的信号关系仿真图。

同步码鉴相器定义为:

二个输入信号形式为“HH”或“LL”即同步码时鉴相器输出信号为高阻态;二个输入信号为非同步码时如果一个规定的输入信号为“H”时输出信号为“H”,否则为“L”。

图1所示的现有高阻型数字鉴相器的内部结构电路中存在着一个同步码鉴相器,只是这一鉴相器的输入信号属于中间态的Qr与Qc,不是输入信号Wr与Wc自身,所以不能成为一个独立的同步码鉴相器。

异步码鉴相器定义为:

二个输入信号形式为同步码的“H”时鉴相器的输出信号为“H”,为同步码的“L”时鉴相器输出信号为“L”;如果二个输入信号形式并不相同即为异步码时鉴相器输出信号为高阻态。

实现形式

图3,图5的异步码鉴相器

对于图3的异步码鉴相器,输入信号WrWc的关系为异步码时标识为1的“异步码检测”检出到则作为控端信号的输出信号断开标识为4的单向模拟开关S2,鉴相器输出为高阻态;否则S2闭合。标识为2的“高电平检出”并不存在具体器件而是直接连接到标识为3的二选一模拟开关S1的控端,如果WrWc=1-(-为任意码)时则S1的公端即S2的输入端与Vcc相接;如果WrWc=0-时则S2的输入端与GND相接。最终,鉴相器输出符合设计定义:WrWc=01=10时输出为高阻态,WrWc=00时输出为“0”态值,WrWc=11时输出为“1”态值。

对于图5这一具体电路形式的异步码鉴相器,当WrWc为异步码时与非门IC1输出为“1”态值则p型场效应管开关断开,或非门IC2输出为“0”态值则n型场效应管开关断开;当WrWc=11时与非门输出为“0”态值则p型场效应管开关导通,或非门输出为“0”态值则n型场效应管开关断开;当WrWc=00时与非门输出为“1”态值则p型场效应管开关断开,或非门输出为“1”态值则n型场效应管开关导通。最终,鉴相器的输出符合设计定义:

WrWc=01=10时输出为高阻态,WrWc=00时输出为“0”态值,WrWc=11时输出为“1”态值。

图2,图4的同步码鉴相器

对于图2的同步码鉴相器,输入信号Wr,Wc的关系为同步码时被标识为1的“同步码检测”检出到则输出信号作为控端信号断开标识为4的单向模拟开关S2,鉴相器输出为高阻态;否则S2闭合。标识为2的“高电平检出”并不存在具体器件而是直接连接到标识为3的二选一模拟开关S1的控端,如果WrWc=1-(-为任意码)时则S1的公端即S2的输入端与Vcc相接;如果WrWc=0-时则S2的输入端与GND相接。最终,鉴相器的输出符合设计定义:WrWc=00=11时输出为高阻态,WrWc=01时输出为“0”态值,WrWc=10时输出为“1”态值。

输入输出信号间的仿真结果关系

同步码鉴相器的输入输出信号间关系,其仿真结果如图6所示,具体各个过程的说明如下:

1)锁定过程:二个信号完全同频,分为二种类型。之一的“反相”类型是指输入信号完全处在异步即相反状态状态,则输出信号的波形与定义中规定的输入信号波形完全一致,符合定义中的关系式。另一的“同相”类型是指输入信号完全处在同步,则输出信号的波形由以下“另2”条款所规定。

2)“定义”过程,二个信号完全同频,输入输出信号间的波形完全符合定义中的规定。

3)初态过程,模拟以本发明的鉴相器构成一个锁相环路在启动时一种常有的单端有输入形式,输入输出信号间的波形关系,分为二种类型。一种是Wr单端有输入,另一种是Wc单端有输入,都完全符合定义中的关系式。

最终,根据《PLL设计的理论与应用》一书及现有锁相环理论中的观点,一个由本发明的鉴相器构成一个锁相环最终在同相同步状态下实现稳定的锁定工作状态。

异步码鉴相器的输入输出信号间关系,其仿真结果如图7所示,具体各个过程的说明如下:

1)锁定过程:二个信号完全同频,分为二种类型。之一的“同相”类型是指输入信号完全处在同步即相反状态状态,则输出信号的波形与输入信号波形完全一致,符合定义中的关系式。另一的“反相”类型是指输入信号完全处在异步,则输出信号的波形由以下“另2”条款所规定。

2)“定义”过程,二个信号完全同频,输入输出信号间的波形完全符合定义中的规定。

3)初态过程,模拟以本发明的鉴相器构成一个锁相环路在启动时一种常有的单端有输入形式,输入输出信号间的波形关系,完全符合定义中的关系式。

最终,根据《PLL设计的理论与应用》一书及现有锁相环理论中的观点,一个由本发明的鉴相器构成一个锁相环最终在同相同步状态下实现稳定的锁定工作状态。

另1,图2,3中括弧内“假性锁定过程”是指理论讨论中以本发明的鉴相器构成一个锁相环路其中一种工作形式,详细内容请参《PLL设计的理论与应用》该书,这里不做讨论与说明。

另2,图6的锁定过程中的“同相”类型,及图7的锁定过程中的“反相”类型,双向箭头标识输出波形,在理论上应是高阻状态下一个在供电位置之间的某一电平值,测试法下则是串联电阻的分压值。但是在实际应用中由于器件的频率特性及锁相环路工作特征的限制,在通用型示波器上所能观察到的波形往往是基于高阻状态即供电位置间电平值下一个正向窄脉冲输出信号波形,或者一个负向窄脉冲输出信号波形,或者一个双向窄脉冲输出信号波形;即为图中标识双向箭头所示。

综合以上内容,基于发明名称为《标准化设计高阻型数字鉴相器的结构原理方案》设计方法中的规定,可以实现电平式高阻型数字鉴相器的设计开发工作的。

企业营业执照

专利注册证原件

身份证

个体户营业执照

身份证

专利注册证原件

专利代理委托书

转让申请书

转让协议

手续合格通知书

专利证书

专利利登记簿副本

提交