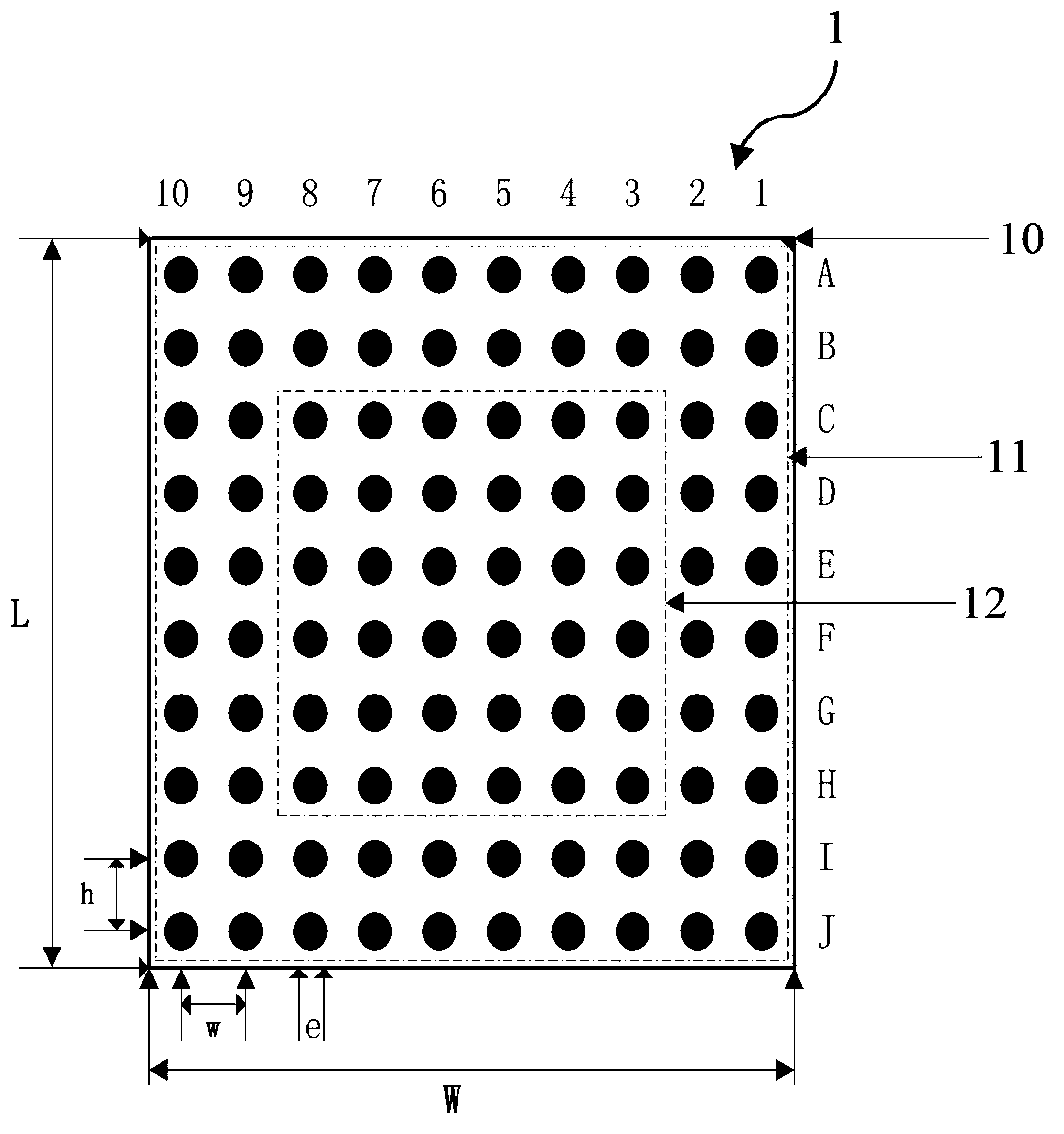

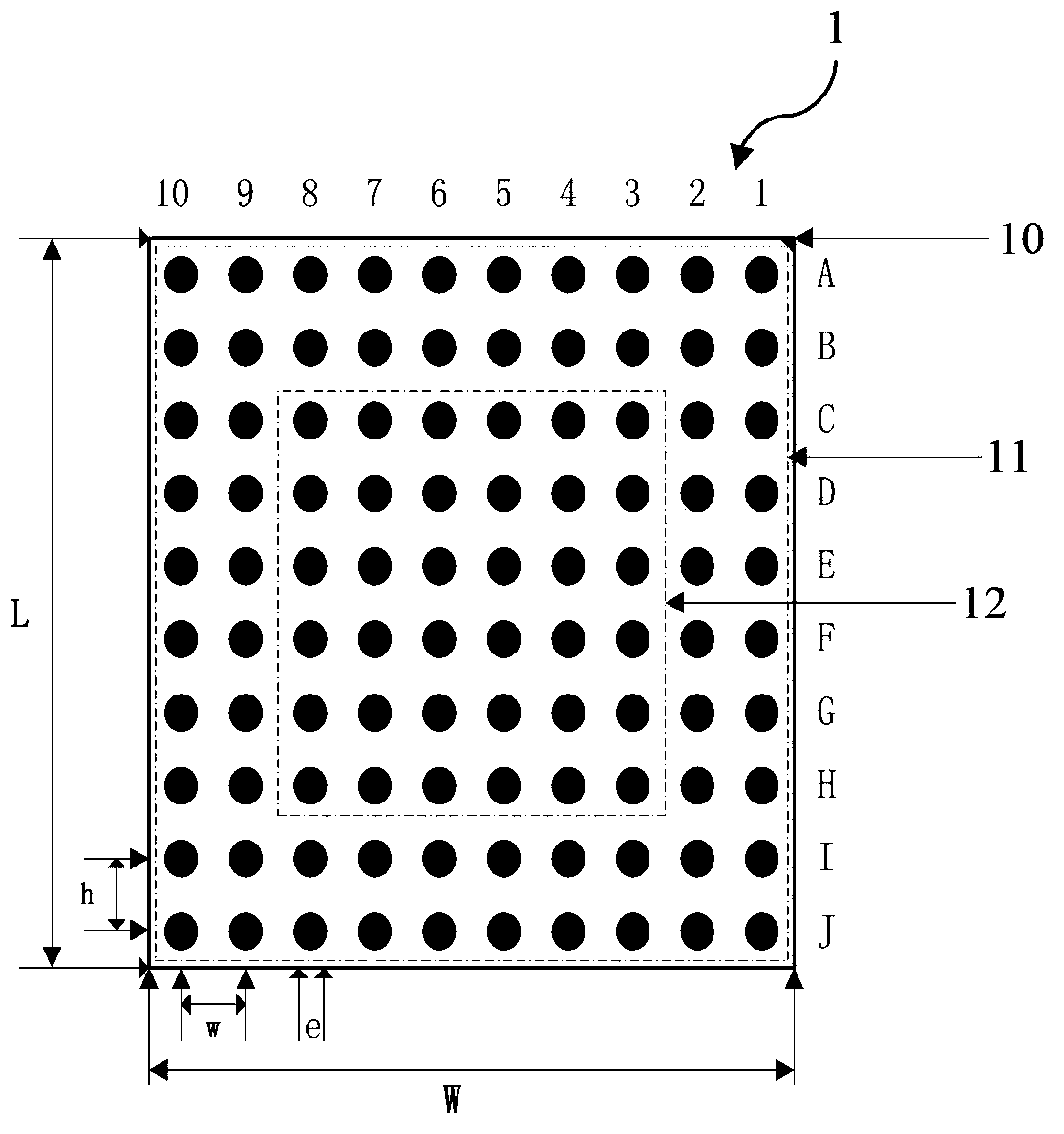

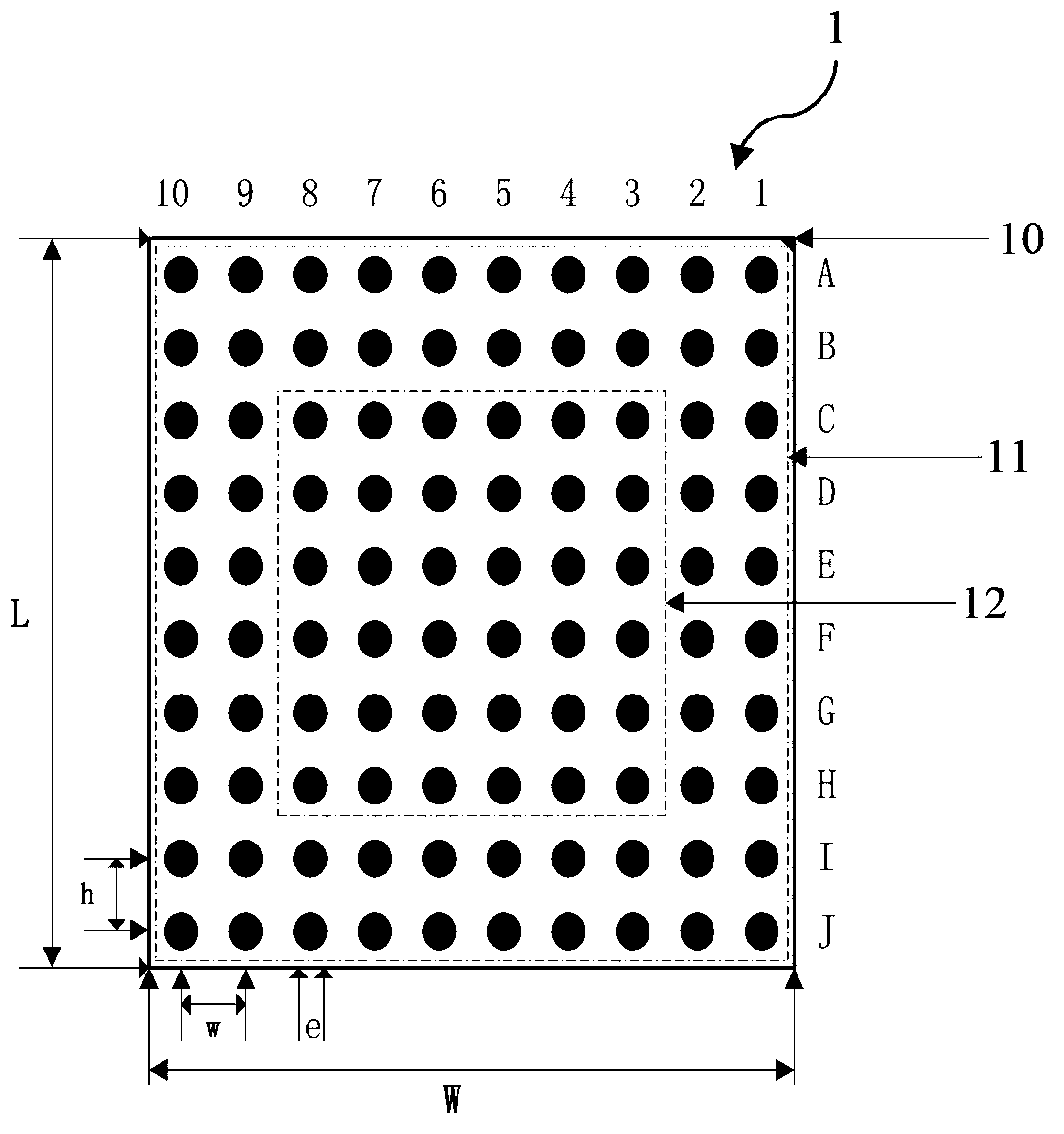

1.一种基板多芯片集成的大端口互连类芯片的实现方法,其特征在于,用多个互连子芯片倒置布放于起互连与支撑作用的基板上表面,通过基板内的多层布线、垂直连接结构、金属接触区、基板与芯片上的相应金属凸点引脚阵列,在基板内实现由多个互连子芯片构成的互连结构的电气与物理连接,同时实现基板的供电网络与基板内多个互连子芯片的供电引脚连接,形成基板内系统供电网络的电气与物理连接,从而实现比所使用的互连子芯片端口数大的而功能相同的基板封装尺度级的等效大端口互连类芯片,其中将基板划分为三个区域:第一布放区域为芯片布放禁止区,该区域为沿基板四边向内扩展的区域,在该第一布放区域内禁止放置第一、二类互连子芯片,可放置面积较小的第三类互连子芯片、无源器件,以便于提高多芯片外接端口与基板底面外接金属凸点连接布线的成功率;第二布放区域与第一布放区域毗连,在该第二布放区域内仅放置第一类或第二类外层互连子芯片、无源器件;第三布放区域与第二布放区域毗连,在该第三布放区域内仅放置第一类或第二类内层互连子芯片、无源器件;该金属凸点阵列引脚被划分为中央区和一个或者多个信号区:中央区的金属凸点引脚位于基板底面金属凸点阵列引脚的中央局域,用于供电引脚;该信号区由中央区外围的相邻二层金属凸点阵列引脚构成,根据总的外接信号数,在基板底面划分出多个环状的信号区,该信号区内的引脚,先分配给高速差分对信号,分配剩余的金属凸点阵列引脚分配给辅助信号及供电引脚,高速差分对引脚之间根据降低引脚间信号干扰的需要插入一定数量的供电引脚;该方法包括布线分群步骤,用于对基板内所有互连子芯片引脚、辅助器件引脚、基板底面金属凸点阵列引脚,按互连关系的相关属性进行布线分群,具体包括:将位于基板上的所有互连子芯片与辅助器件引脚分为3个布线引脚群,所有基板内的互连子芯片与相关的辅助器件的电源与接地引脚、基板引脚阵列中的电源与接地引脚,分为第一布线引脚群;其中所有外层互连子芯片需外接的互连端口引脚以及相关的辅助器件的相应引脚分为第二布线引脚群;其余的引脚分为第三布线引脚群,其中包括所有外层互连子芯片内端口引脚、与其有互连关系的所有内层互连子芯片端口引脚、有互连关系的内层互连子芯片端口相应引脚以及芯片辅助引脚、相关的辅助器件的引脚;该互连结构按如下生成规则生成:选用p端口的互连子芯片(3/2)p个,得到端口数为N=(1/2)p2的最大二级等效互连结构;或该互连结构按如下生成规则生成:选用p端口的互连子芯片(4/3)p个,得到端口数为(4/9)p2的最大二级等效互连结构,其中p=3q,q为正数;或该互连结构按如下生成规则生成:选用r1行、c1列的p端口互连子芯片,得到端口数为(2r1+2c1)(p-5)-4p+28的等效二维全互连结构,r1和c1为正整数。

2.如权利要求1所述基板多芯片集成的大端口互连类芯片的实现方法,其特征在于,对于所使用的互连子芯片:属于外层互连子芯片的该第一类或第二类互连子芯片,放置于该第二布放区域;属于内层互连子芯片的该第一类或第二类互连子芯片,只可放置于该第三布放区域的基板的内层区域。

3.如权利要求1所述基板多芯片集成的大端口互连类芯片的实现方法,其特征在于,在该信号区内,对需要构成差分信号对的引脚,按直接上下凸点引脚构成一对差分信号对的规则,在信号层内逐次分配;先使用最外侧信号区,该区内的基板凸点引脚分配完后,再使用次内侧信号区,直至完成所有差分信号引脚对的分配。

4.如权利要求1所述基板多芯片集成的大端口互连类芯片的实现方法,其特征在于,该方法包括划分布线区步骤,用于对基板内的可布线资源进行布线分区并分配给相应的布线引脚群具体包括:将基板的布线表面与其下覆盖的布线层划分为三个布线区,第一布线区为整个基板的全部可布线区域与布线资源,第一布线引脚群先使用该布线区;第二布线区为基板外层芯片中线框到基板外边缘内的可布线区与布线资源,相对第三布线引脚群,第二布线引脚群先使用该布线区;第三布线区为外层芯片中线框以内的基板区域与布线资源,相对第二布线引脚群,第三布线引脚群先使用该布线区。

5.如权利要求4所述基板多芯片集成的大端口互连类芯片的实现方法,其特征在于,该方法包括处理布线步骤,具体包括:(1)处理第一布线群,该布线群内的引脚以最短连线原则,先行布通;(2)处理第二布线群内的引脚,该布线群先使用第二布线区内的布线资源,先与基板底部最外侧环状圈内的信号引脚布通,逐次使用内侧环状圈内的信号引脚,直至布通所有外层互连子芯片的外接端口引脚,当第二布线区资源短缺时,可以适当借用第三布线区资源;(3)第三布线群首先使用第三布线区布线资源完成外层互连子芯片端口引脚与内层互连子芯片引脚间的相应连接布线,然后完成内层互连子芯片端口间相应引脚的连接布线,最后设法完成辅助引脚的连接布线;(4)当第三布线区布线资源短缺时,在保证第二布线区布线的情况下,可从第二布线区借用相应的布线资源;(5)布局、引脚分配、布线三部分相互迭代。

6.一种基板多芯片集成的大端口互连类芯片的实现方法,其特征在于,包括如下步骤:步骤1、选定互连子芯片硅晶圆;步骤2、在硅晶圆表面生长互连子芯片引脚的金属凸点,备选出功能符合要求的、经切割后的裸互连子芯片;步骤3、按具体需求,选定等效大端口互连芯片生成规则,构建具体的基板多芯片集成用的互连结构,确定每个基板使用的裸互连子芯片数目及相应的辅助器件;步骤4、根据使用的互连子芯片、等效互连芯片的端口的具体规格参数,确定基板的初始参数;步骤5、根据互连子芯片、互连结构、基板参数,开始基板布局;步骤6、基板底面金属凸点接触引脚阵列划分与引脚分配;步骤7、基板高速差分对引脚与普通信号引脚分配;步骤8、根据上述基板多芯片的布局规则、基板底部金属凸点引脚分区与分配规则,将位于基板上的多芯片的引脚划分布线群;将整个基板的布线表面与布线层划分布线区;步骤9、根据最后基板内多芯片的布局、引脚阵列分配、布线分区,完成基板布线,将设计好的基板设计提交基板厂家生产出合格的基板;步骤10、将互连子芯片与多层布线基板封装,完成相应的测试及系统验证,得到最终的基板多芯片集成的大端口互连类芯片;其中将基板划分为三个区域:第一布放区域为芯片布放禁止区,该区域为沿基板四边向内扩展的区域,在该第一布放区域内禁止放置第一、二类互连子芯片,可放置面积较小的第三类互连子芯片、无源器件,以便于提高多芯片外接端口与基板底面外接金属凸点连接布线的成功率;第二布放区域与第一布放区域毗连,在该第二布放区域内仅放置第一类或第二类外层互连子芯片、无源器件;第三布放区域与第二布放区域毗连,在该第三布放区域内仅放置第一类或第二类内层互连子芯片、无源器件;该金属凸点阵列引脚被划分为中央区和一个或者多个信号区:中央区的金属凸点引脚位于基板底面金属凸点阵列引脚的中央局域,用于供电引脚;该信号区由中央区外围的相邻二层金属凸点阵列引脚构成,根据总的外接信号数,在基板底面划分出多个环状的信号区,该信号区内的引脚,先分配给高速差分对信号,分配剩余的金属凸点阵列引脚分配给辅助信号及供电引脚,高速差分对引脚之间根据降低引脚间信号干扰的需要插入一定数量的供电引脚;该方法包括布线分群步骤,用于对基板内所有互连子芯片引脚、辅助器件引脚、基板底面金属凸点阵列引脚,按互连关系的相关属性进行布线分群,具体包括:将位于基板上的所有互连子芯片与辅助器件引脚分为3个布线引脚群,所有基板内的互连子芯片与相关的辅助器件的电源与接地引脚、基板引脚阵列中的电源与接地引脚,分为第一布线引脚群;其中所有外层互连子芯片需外接的互连端口引脚以及相关的辅助器件的相应引脚分为第二布线引脚群;其余的引脚分为第三布线引脚群,其中包括所有外层互连子芯片内端口引脚、与其有互连关系的所有内层互连子芯片端口引脚、有互连关系的内层互连子芯片端口相应引脚以及芯片辅助引脚、相关的辅助器件的引脚;该互连结构按如下生成规则生成:选用p端口的互连子芯片(3/2)p个,得到端口数为N=(1/2)p2的最大二级等效互连结构;或该互连结构按如下生成规则生成:选用p端口的互连子芯片(4/3)p个,得到端口数为(4/9)p2的最大二级等效互连结构,其中p=3q,q为正数;或该互连结构按如下生成规则生成:选用r1行、c1列的p端口互连子芯片,得到端口数为(2r1+2c1)(p-5)-4p+28的等效二维全互连结构,r1和c1为正整数。

7.一种采用上述权利要求1-6任意一项方法的基板多芯片集成的大端口互连类芯片。

展开

北京

北京

微信公众号 扫一扫 关注我们

微信公众号 扫一扫 关注我们