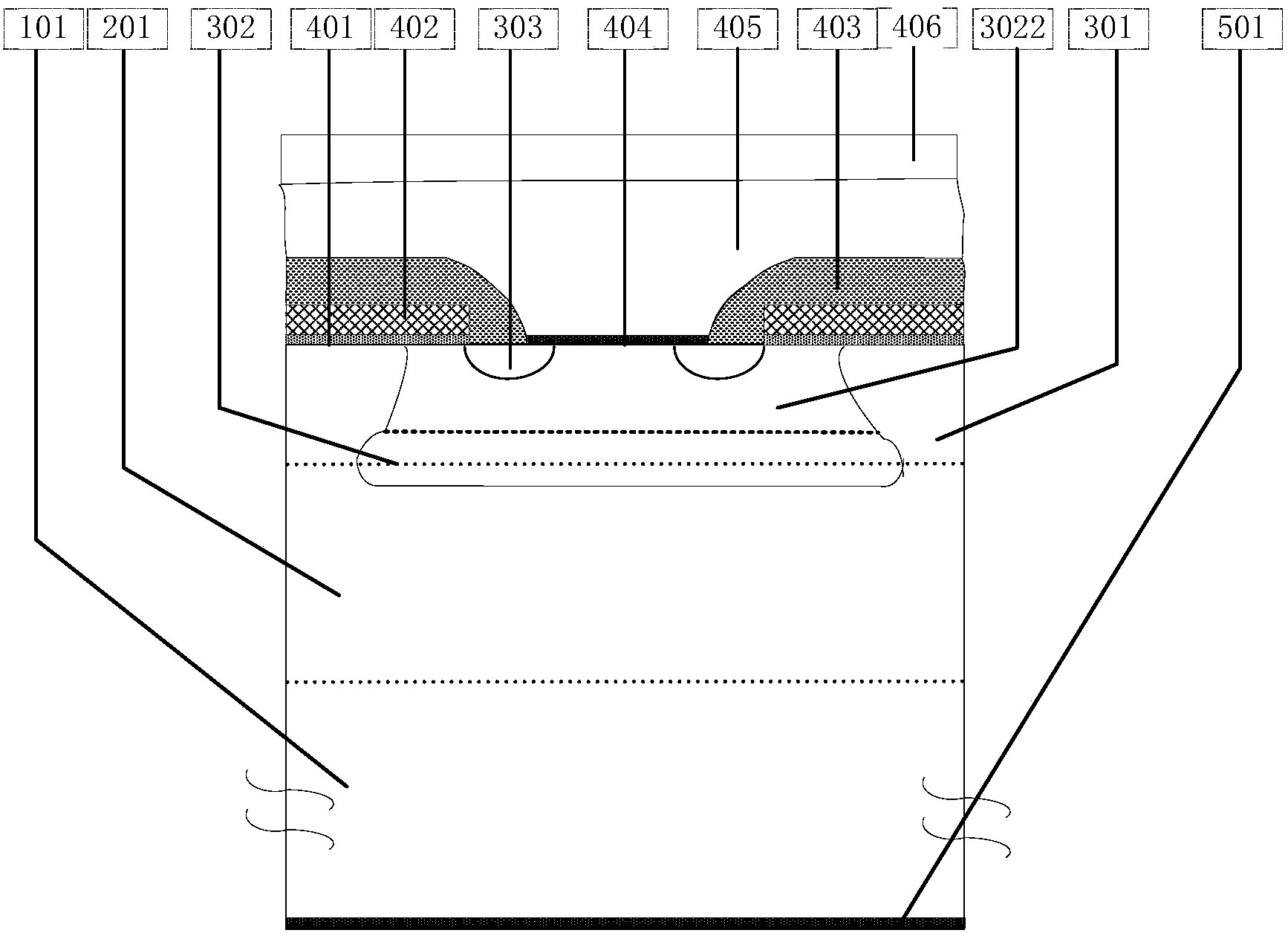

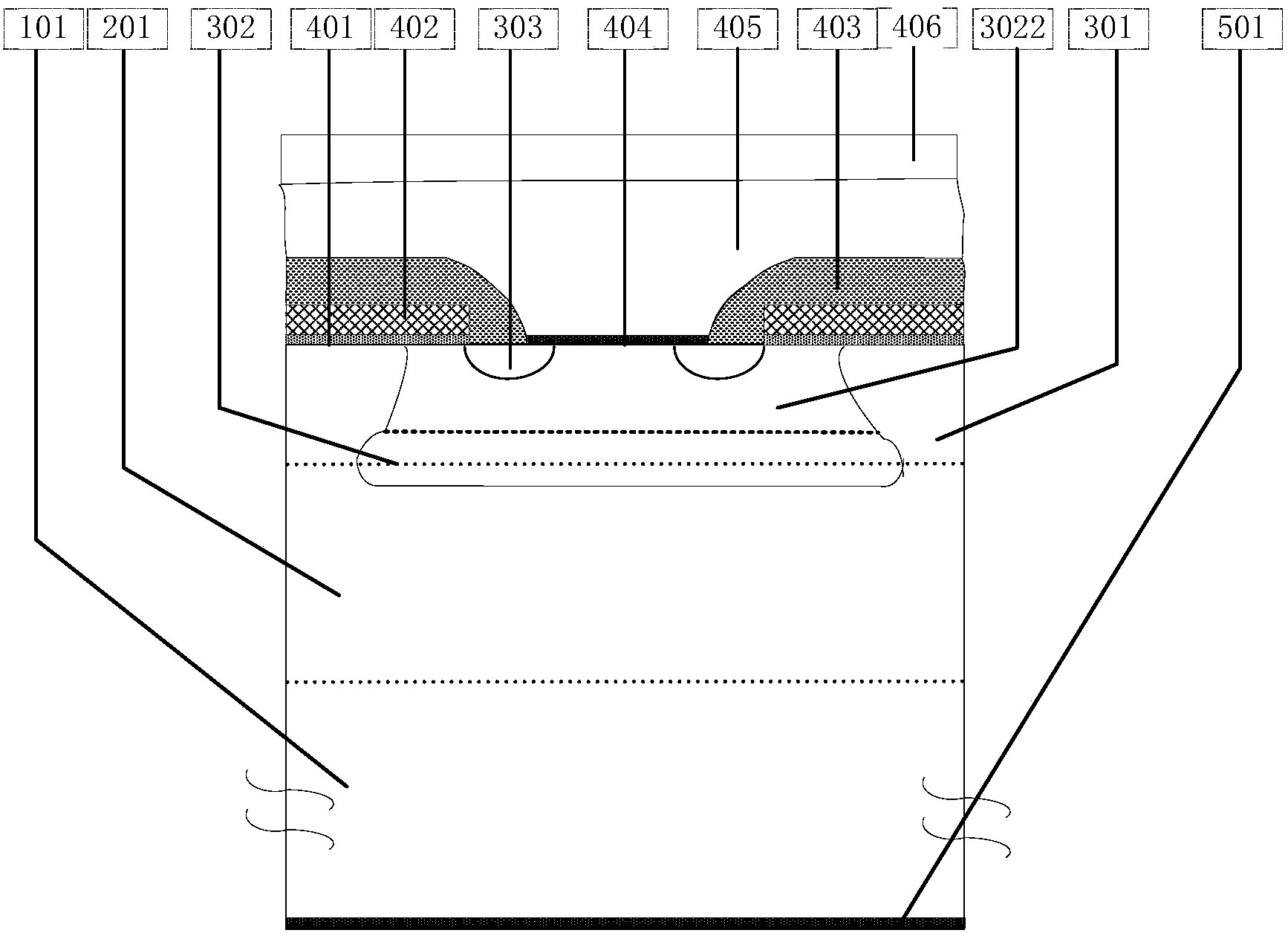

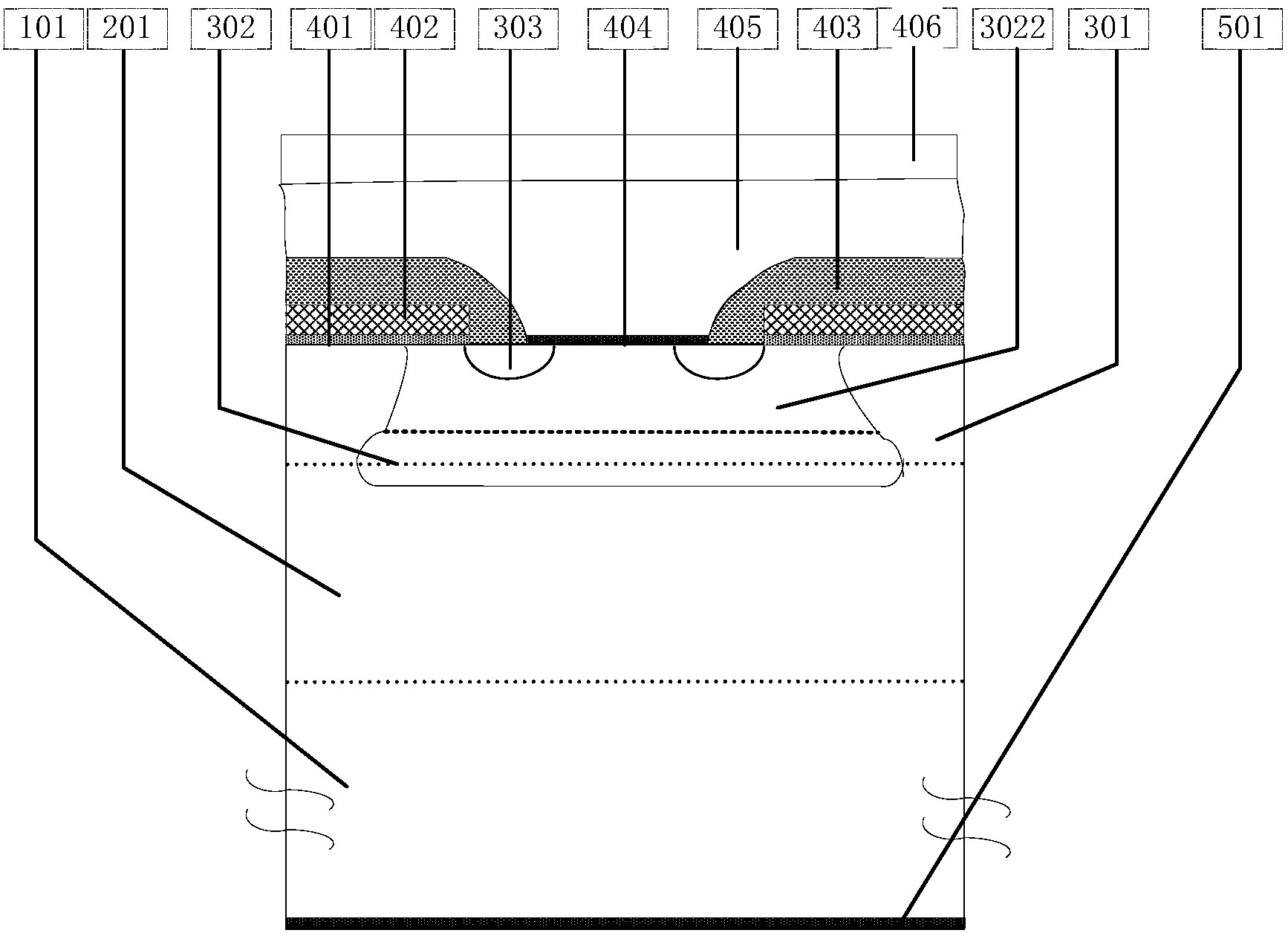

1.一种基于倒阱工艺的功率MOSFET器件,它包括衬底材料,其特征在于:所述衬底材料上覆盖有第一外延层;第一外延层上覆盖有第二外延层;轻掺杂第一导电类型第一外延层(201)位于第一外延层和第二外延层之间;所述衬底材料覆盖在漏极金属层(501)上;所述衬底材料为重掺杂第一导电类型衬底材料(101);第一外延层为轻掺杂第一导电类型第一外延层(201);第二外延层为轻掺杂第一导电类型第二外延层(301);重掺杂第一导电类型衬底材料(101)覆盖于漏极金属层(501)之上;所述轻掺杂第一导电类型第一外延层(201)覆盖于重掺杂第一导电类型衬底材料(101)之上;所述轻掺杂第一导电类型第二外延层(301)覆盖于轻掺杂第一导电类型第一外延层(201)之上;轻掺杂第一导电类型第一外延层(201)的厚度d1为传统VDMOS器件外延层厚度D减去氧化工艺消耗部分D1、第二导电类型体区(3022)结深D2的厚度,即:d1=D-D1-D2;轻掺杂第一导电类型第一外延层(201)是均匀掺杂或是从重掺杂第一导电类型衬底材料(101)上表面到轻掺杂第一导电类型第一外延层(201)上表面的缓变掺杂。

2.根据权利要求1所述的一种基于倒阱工艺的功率MOSFET器件,其特征在于:重掺杂第二导电类型埋层(302)介于轻掺杂第一导电类型第二外延层(301)和轻掺杂第一导电类型第一外延层(201)之间,重掺杂第二导电类型埋层(302)嵌入第一导电类型第一外延层(201)和第一导电类型第二外延层(301)内部;第二导电类型体区(3022)在轻掺杂第一导电类型第二外延层(301)内部,第二导电类型体区(3022)的结深大于第一导电类型第二外延层(301)的厚度;第二导电类型体区(3022)的上表面为第一导电类型第二外延层(301)的上表面的一部分;第二导电类型体区(3022)的上表面宽度小于第二导电类型体区(3022)的下结面宽度;重掺杂第一导电类型源区(303)在第二导电类型体区(3022)内部;重掺杂第一导电类型源区(303)的深度小于第二导电类型体区(3022)的深度;重掺杂第一导电类型源区(303)的上表面为第二导电类型体区3022的部分上表面;重掺杂第一导电类型源区(303)的上表面与第二导电类型体区(3022)内重掺杂第一导电类型源区(303)之间的上表面依次覆盖接触金属层(404)、金属层(405)和钝化介质层(406);所述第二导电类型体区(3022)的上表面和第二导电类型体区(3022)之间的表面,从下到上依次覆盖栅介质层(401)、多晶硅栅介质层(402)、ILD介质层(403)、金属层(405)和钝化介质层(406)。

3.根据权利要求1所述的一种基于倒阱工艺的功率MOSFET器件,其特征在于:重掺杂第二导电类型埋层(302)位置为第二导电类型体区(3022)在轻掺杂第一导电类型第一外延层(201)上表面的投影位置,且重掺杂第二导电类型埋层(302)的长度大于第二导电类型体区(3022)上表面在轻掺杂第一导电类型第一外延层(201)上表面投影的长度。

4.根据权利要求1所述的一种基于倒阱工艺的功率MOSFET器件,其特征在于:第二导电类型体区(3022)由二个以上重复的结构单元组成;第二导电类型体区(3022)是通过重掺杂第二导电类型埋层(302)在高温下扩散形成;第二导电类型体区(3022)杂质浓度的分布峰值在第二导电类型体区(3022)结深的3/4位置。

5.根据权利要求1所述的一种基于倒阱工艺的功率MOSFET器件,其特征在于:它还包括第二导电类型终端PN结;所述第二导电类型终端PN结的形状、掺杂与第二导电类型体区3022一致;最内环包围的中间区域为器件的有源区。

展开

北京

北京

微信公众号 扫一扫 关注我们

微信公众号 扫一扫 关注我们